三星创了记录,8400亿人民币砸出个3纳米良品率为零?

作 者 | Rickzhang

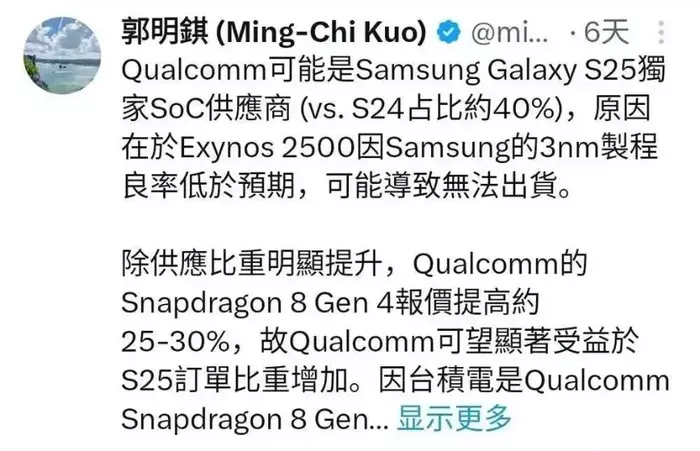

6月19日,一则消息在科技圈内引起了轩然大波。知名分析师郭明錤在个人社交媒体上爆料,由于三星自家的Exynos 2500芯片良率远低于预期,导致无法按时出货,高通将取而代之,成为三星Galaxy S25系列机型的独家SoC供应商。这一变化,无疑给三星的半导体业务蒙上了一层阴影。

回溯到上一代Galaxy S24机型,高通处理器芯片仅占据了40%的市场份额,而剩余的60%则由三星自研芯片占据。三星Galaxy S24和S24+搭载的便是三星自家研发的Exynos 2400 4纳米芯片,其技术实力可见一斑。然而,当三星试图跨越到更先进的3纳米工艺时,却似乎遭遇了技术瓶颈。

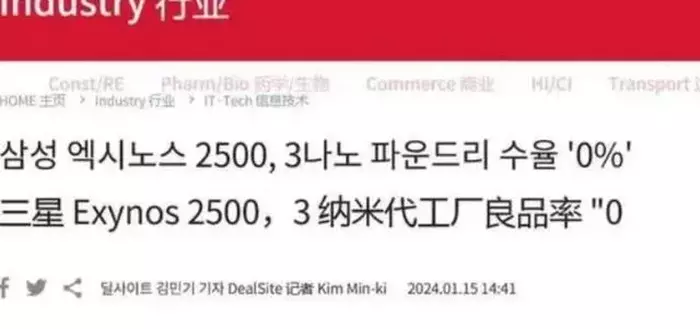

此前,韩媒DealSite的一份爆料更是令人咋舌:三星在试生产Exynos 2500处理器时,其3纳米工艺的良率竟然为0%。这一消息虽令人难以置信,但却与郭明錤的爆料不谋而合,引发了业界对三星3纳米工艺良率的广泛质疑。

三星的3纳米 GAA工艺难产,不仅影响了Exynos 2500处理器的生产,更波及到了后续产品,如Galaxy Watch 7的芯片组也无法实现量产。这一连锁反应,对三星的半导体业务乃至整个电子产品线都造成了不小的冲击。

其实,早在去年12月,就有业内人士爆料称,高通因三星3纳米良率不佳,已取消原计划由三星作为第二供应商的策略,转而选择台积电独家代工其下一代处理器Snapdragon 8 Gen4。这一决策转变,无疑是对三星3纳米工艺良率问题的又一有力佐证。

面对外界的种种质疑,三星总部回应称,3纳米的良率和客户相关信息均为敏感信息,无法透露。同时,公司也表示,目前3纳米芯片工艺在良率和性能表现上正不断成熟,并计划于今年晚些时候推出第二代3纳米工艺,以期挽回市场信心。

然而,三星在3纳米工艺上的巨额投资却不容忽视。据财报显示,三星在全年资本支出中,有近半数资金用于半导体领域。而在整个3纳米项目中,三星更是投入了高达1160亿美元,折合近8400亿人民币。这还不包括后续两座3纳米工厂的建设费用。

如此巨大的投入,如今却面临着良率低迷的困境,无疑给三星带来了巨大的压力。

而根据三星电子披露的2023年全年的业绩报告来看,三星营业利润较上年同期下降84.9%,全年营收下降14.3%,全年净利润下降72.2%。其中,受损最大的自然是半导体业务,2023年损失14.9 万亿韩元。

因此,三星在3纳米工艺上面临的良率问题,已成为其半导体业务发展的一大桎梏。

寄以厚望的3纳米

最近一场关于三纳米(3nm)工艺制程的豪赌,却让这家巨头企业陷入了前所未有的困境。

曾几何时,三星宣布全球首家量产3纳米芯片,这一消息如同科技界的一声惊雷,震撼了所有人。Exynos 2500,这款基于三星3纳米工艺制程的芯片,被寄予了厚望。它的设计目标直指高端设备市场,旨在以全新的Cortex-X5核心和Cortex-A730核心,为用户带来前所未有的性能体验。与上一代Exynos 2400相比,性能提升的预期让人充满期待。

现实却给了三星一记重拳。在试产阶段,Exynos 2500未能通过质量测试,这一突如其来的挫败不仅让这款芯片的前景蒙上了阴影,更导致后续的Galaxy Watch 7的芯片组也无法量产。对于三星来说,这无疑是一次重大的挫败,尤其是在与台积电的半导体工艺制程竞争中,这一挫败更显得尤为刺眼。

三星的3纳米工艺技术,在业界曾被视为一项重大突破。与台积电在2纳米工艺制程上才会转向GAA晶体管的保守策略相比,三星在第一代3纳米工艺上就大胆地采用了GAA晶体管技术,而且是MBCFET多桥通道场效应晶体管,这一技术被称为SF3E,也就是3GAE工艺。

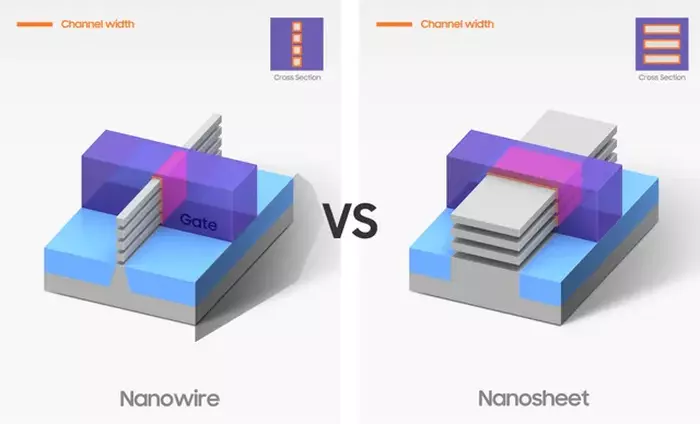

这种技术采用了更宽通的纳米片,与采用窄通道纳米线的GAA技术相比,能提供更高的性能和能耗比。GAA的设计灵活性对设计技术协同优化(DTCO)非常有利,有助于实现更好的PPA(性能、功率和面积)优势。

然而,理想很丰满,现实却很骨感。

尽管三星的3纳米工艺在技术上有着诸多优势,但量产良率的不理想却让其陷入了尴尬的境地。2022年12月,台积电宣布量产3纳米后,就陆续有韩国媒体曝出,三星实际量产良率远远落后于台积电。根据《金融时报》的报道,三星生产3纳米芯片中最基础的产品良率当时仅为60%,这一数字远低于客户的预期,也导致三星迟迟没能拿下高通、谷歌等大客户的订单。

与之形成鲜明对比的是,台积电虽然落后三星近半年发布3纳米工艺,但其良率与规模却在稳步提升。

目前,三星尚未就这一事件发表正式声明。但业界普遍认为,如果三星无法尽快解决这一问题,其将面临巨大的商业风险。在半导体行业,时间就是金钱,每一分钟的延误都可能意味着数百万美元的损失。而对于三星来说,这场关于3纳米的豪赌,无疑已经让其陷入了深深的困境之中。

放不下的GAA

在这个科技日新月异的时代,有一项技术如同未来电子设备的心脏,它就是GAA技术,全称Gate-All-Around,中文意为“全环绕栅极”。这不仅仅是一项技术,更是推动摩尔定律继续前行的引擎。然而,当我们深入探究这项技术时,也不得不面对它所带来的挑战与困境。

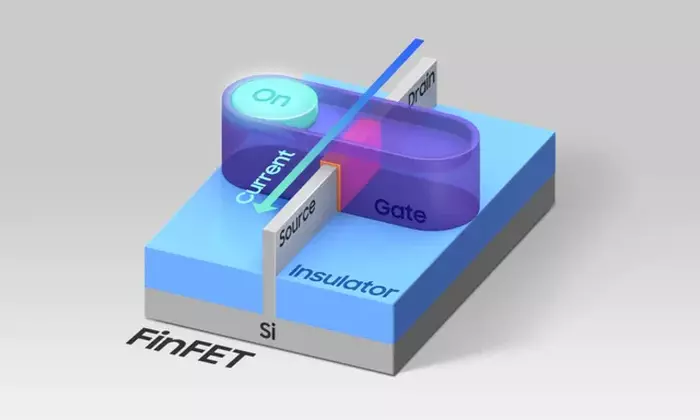

回想1965年,英特尔的联合创始人戈登·摩尔提出了一个震撼业界的预言:集成电路上可容纳的晶体管数量大约每两年翻一番。这个预言,被后人称为“摩尔定律”,它如同科技界的灯塔,指引着半导体行业不断前行。然而,随着我们逼近物理的极限,传统的FinFET技术已经难以满足摩尔定律那日益增长的需求。这时,GAA技术挺身而出,成为了摩尔定律的新守护者。

GAA技术,这是一种先进的晶体管设计。与传统的FinFET技术相比,GAA的栅极完全环绕在晶体管的通道周围,如同一把锋利的剑,剑刃(晶体管的通道)被剑身(栅极)紧紧环绕。这种设计提供了更好的电流控制能力,可以显著提高晶体管的性能,降低功耗,并允许在更小的空间内集成更多的晶体管。

然而,技术的进步总是伴随着挑战。为了获得最好的性能、功率和面积(PPA),我们不仅使晶体管更小,而且还改变了其结构。GAA技术就是在侧面铺设FinFET的鳍片(Si场像鱼鳍一样隆起的区域)的片状结构。将这些薄片垂直堆积起来,我们可以使更大的电流在具有相同水平面积的晶体管中流动。但这也带来了工艺上的复杂性,尤其是纳米线GAA,必须堆叠更多的线层以增加总沟道宽度。

在这场科技竞赛中,三星选择了GAA技术作为其突破3纳米工艺的关键。三星的GAA技术,被称为MBCFET(Multi-Bridge-Channel FET),它通过在纳米尺度上构建多个栅极桥接,实现了对电流的更精细控制。然而,这项技术的推进并非一帆风顺。

尽管GAA技术能够提供比FinFET更高的性能,预计在3纳米工艺中,性能提升可达30%以上;在功耗方面,相较于FinFET,能够实现25%以上的降低。但是,技术的飞跃也带来了前所未有的挑战。从5纳米到3纳米,晶体管的尺寸缩小了40%,这是一个巨大的飞跃,也是一个巨大的考验。

虽然GAA技术,以其独特的栅极设计,完全环绕晶体管的通道,仿佛给晶体管穿上了一层“紧身衣”。这一创新设计确实带来了性能的显著提升和功耗的降低。三星更是将其视为突破3纳米工艺的关键,倾力打造了MBCFET(Multi-Bridge-Channel FET)。然而,这场技术革命的背后,却隐藏着巨大的风险和不确定性。

想象一下,你在一个繁忙的十字路口,如果只有红绿灯控制交通,那么效率必然受限。但是,如果每个方向都有专门的交通管理员,他们可以实时监控并优化车流,那么交通就会变得无比顺畅。GAA技术就像是这些交通管理员,它们在纳米尺度上指挥着电子的流动,确保了数据传输的高速和高效。然而,这些“交通管理员”的训练和管理,却需要极高的工艺和投入。

三星的MBCFET技术虽然创新,但也面临着工艺复杂、成本高昂等问题。纳米线GAA需要堆叠更多的线层,这使得工艺更加复杂,生产成本也随之上升。而对于片状结构的GAA,虽然可以简化工艺,但也需要更大的宽度,这在一定程度上限制了晶体管的密度。

更为严峻的是,随着技术的不断推进,物理极限的制约也日益凸显。即使有了GAA技术,我们是否能够继续遵循摩尔定律的步伐,每两年翻一番,仍然是一个未知数。

另外最新消息显示,美国正考虑限制中国获得GAA的相关芯片制造技术,希望最终可以阻止中国获取用于3纳米及以下生产所需的设备。

路可能走错了

其实不管是台积电的FinFET还是三星的GAA,骨子里都是通过堆资源生生在单位面积上摊入更多的晶体管,以达到推动芯片性能提升的目标。

实际上,从阿斯麦透露的光刻机波长计算可以看出,不论是三星还是台积电,其实际意义上已经没有栅极宽度的计量单位,所谓3纳米更像是对于某种程度上芯片晶体管密度数值的定义。

从真正使用过程中看,芯片只要达到单位面积上晶体管密度追上台积电或者三星所谓3纳米、5纳米的方案,芯片性能不会差这两家推出的芯片多少。

因此,真正要解决的其实是如何提升单位面积上可能容纳的晶体管数量。而根据电子隧穿理论,现在的晶体管栅极宽度,已经挡不住电子,产生大量的能源浪费和发热。从这个角度上看,不论是三星还是台积电,做出的3纳米芯片,能耗高、发热大是必然结果。

所以,从这点来说,他们选择的技术路线可能有问题。而这种技术路线,还特别吃资源,要有极深紫外的光刻机,要有最高标号的光刻胶、浸没式的后道蚀刻设备等等,也让投资十分巨大,稍有不慎就会出现三星目前面临的困境。

反观国内芯片产业,尤其是以华为为代表的先进芯片制造业,其实已经走出自己的一条道路,抛弃了三星和台积电走的所谓主流通路,围绕增加单位面积的晶体管数量来做文章,通过大量使用新架构、新封装工艺等方式,不光利用现有条件推出高性能芯片,还在不断推动芯片性能的增长。

尤其华为在芯片领域公布的一系列设计、制造专利,都是为了提升晶体管密度准备,目标明确,而且有些非常天马行空却又有实施可行性,实属难得。

在这种情况下,估计再有2-3年,我们的高端芯片产业会走出不同于三星、台积电的另一条道路,甚至绕过摩尔定律的限制,推动中国芯片性能的提升。

这是科技和创新的力量,也是自力更生的奇迹。